## PATENT SPECIFICATION

DRAWINGS ATTACHED

Date of filing Complete Specification June 20, 1958.

Application Date March 22, 1957.

Complete Specification Published Oct. 28, 1959.

No. 9568/57.

Index at acceptance: —Class 40(6), N(1A1:2A).

International Classification: -H03f.

#### COMPLETE SPECIFICATION

# Improvements in or relating to Voltage Limiting Apparatus

We, CHARLES GILBERT MAYO, a British Subject, of 16, Christchurch Road, Purley, Surrey, EDMUND RAMSAY WIGAN, a British Subject, of "Kerry", Barnham, Sussex, and ROY EDWARD JONES, a British Subject, of 48, Kingscroft Road, Leatherhead, Surrey, do hereby declare the inventioon, for which we pray that a patent may be granted to us, and the method by which it is to be performed, to 10 be particularly described in and by the following statement:

The invention relates to voltage limiting apparatus, for example limiters for suppressing unwanted amplitude modulation in FM

15 wireless receivers.

The invention provides voltage limiting apparatus comprising a tuned tank circuit, having an impedance which is low except at its resonant frequency, and a biassed diode or like rectifier device fed from the tank circuit through at least one rejector circuit tuned to a harmonic of the resonant frequency of the tank circuit.

A specific circuit for voltage limiting in a 25 FM wireless receiver and embodying the invention will now be described by way of example and with reference to the accompanying drawings in which:-

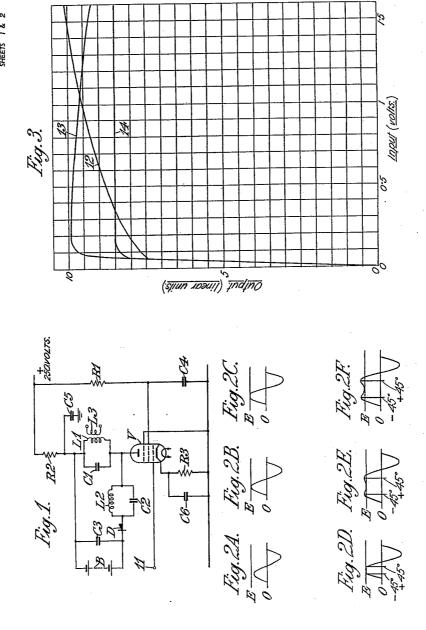

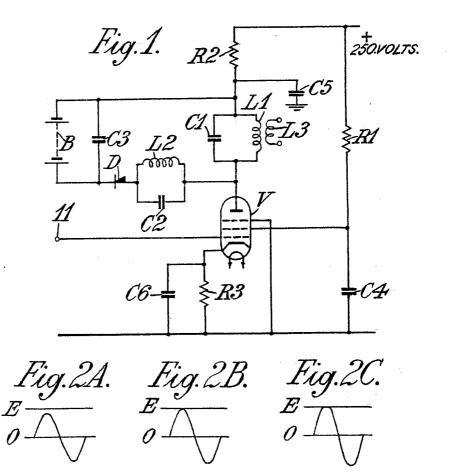

Figure 1 is a diagram of the circuit;

Figures 2A—2F indicates the wave-form of the voltage across the diode in various circumstances, and

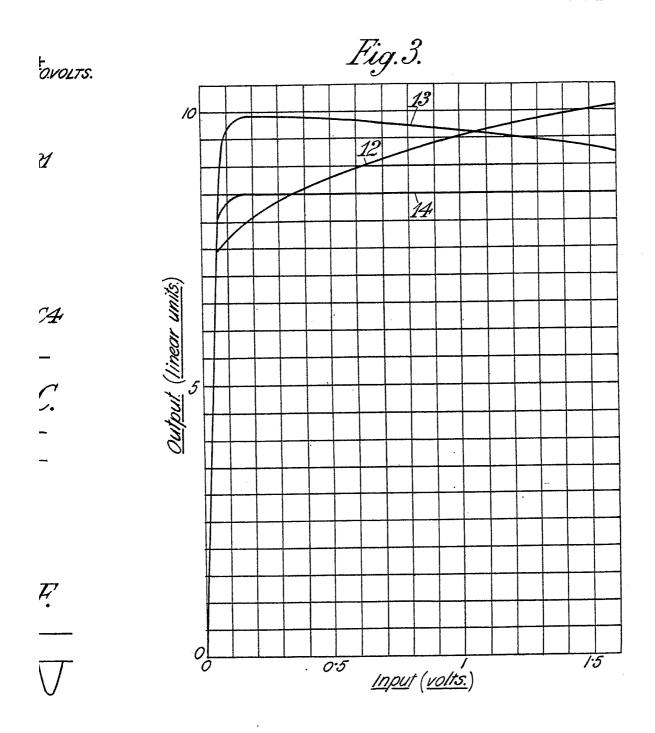

Figure 3 shows the output/input charac-

teristics of the circuit.

The circuit comprises a pentode amplifier valve V having an input applied to its control grid from the input terminal 11. The anode circuit of the valve V includes a tuned parallel tank circuit L1, C1 from which a diode D is fed through a tuned parallel rejector circuit L2, C2. The diode is biassed by a dry-cell battery B, or other well-known means of providing constant voltage. The bias voltage for the diode may alternatively be provided wholly or in part by rectified current delivered by the diode itself. The output

of the circuit is taken from the coil L3 which is inductively coupled to the inductance L1 of the tank circuit.

In this example the valve V is operated under conditions giving a mutual conductance of about 7mA/volt and the tank circuit is tuned to a frequency of 10.7 Mc/s. The rejector circuit L2, C2 is tuned either to the second harmonic of the signal frequency (i.e. 21.4 Mc/s) or to the third harmonic of the signal frequency (i.e. 32.1 Mc/s). In each case the inductance L2 is tuned partly by stray capacity and partly by the capacitor C2. When the rejector circuit is tuned to the second harmonic its coil L2 has a Q of 143, and when the rejector circuit is tuned to the third harmonic its coil has a Q of 115.

If the rejector circuit L2, C2 were omitted

and the tank circuit L1, C1 were to be replaced by a resistive load the effect of the diode D would be to distort the voltage waveform by clipping its positive-going half cycles whenever their amplitude exceeded the bias on the diode. If the tank circuit were employed with the rejector circuit omitted, the tank circuit would tend to maintain the output voltage wave-form as a sinusiodal wave-form in spite of any control action introduced by the diode, owing to the relatively low impedance of the tank circuit at the harmonic frequencies. The diode would in that case act merely as a resistive load varying with the input.

In the circuit shown in Figure 1 however the diode D is sepaarted from the tank circuit by the parallel tuned rejector circuit L2, C2, so that the voltage across the diode circuit is not constrained by the relatively low impedance of the tank circuit at the harmonic fre- 85 qeuncies. That voltage can therefore have a cilpped wave-form, even though the wave-form across the tank circuit remains substantially undistorted.

The wave-form of the voltage across the diode D is indicated approximately in Figures 2A-2F for the case in which the rejector

circuit is tuned to the second harmonic, In Figures 2A—2F the level of the bias voltage on the diode D is indicated by the line E. In Figure 2A the voltage across the diode is a pure sine wave as its maximum value M is less than E and consequently the diode D would not conduct even in the absence of the rejector circuit. In Figure 2B the waveform is also sinusiodal, but the diode would conduct instantaneously at the positive-going peaks if the rejector circuit were absent. In Figure 2C, which is appropriate to the case when the peak value M of the voltage applied to the diode is between E and  $E\sqrt{2}$ , the diode 15 would conduct for the period during which the positive-going part of the wave-form is greater than E, but the presence of the rejector circuit prevents conduction by the diode during that period. Figures 2D—2F indicate the 20 nature of the wave-forms when M is equal to, or greater than,  $E\sqrt{2}$ . In the cases of Figures 2E and 2F there is appreciable diode current. In the case when the rejector circuit is tuned to the third harmonic, the limiting voltage at which diode current begins would be approximately  $2E/\sqrt{3}$ . In Figure 3, the line 12 indicates the output/input characteristic with the rejector circuit L2, C2, omitted (i.e., replaced by a

put/input characteristic with the rejector circuit L2, C2, omitted (i.e., replaced by a simpled conductor), the line 13 indicates that characteristic when the rejector circuit is tuned to the second harmonic, and the line 14 indicates the characteristic when the rejector circuit is tuned to the third harmonic. In the case of each of those characteristics, both the input and the output are measured as r.m.s. values at the signal frequency of 10.7 Mc/s.

In this example, the various circuit compared to the compared to the part of the

In this example, the various circuit components have the following values or other details:—

When tuned to second harmonic 12 13 microhenries C2 4 picafarads

statement: -

When tuned to third harmonic 5.3 microhenries 4.5 picafarads R1 33000 ohms R2 3300 ohms

R3 180 ohms

C4 0.01 microfarad C5 0.01 microfarad

C6 0.01 microfarad

V pentode valve type EF80

D germanium diode, gold bonded, Mullard type OA5

50

55

60

80

L1 and C1 are a conventional tuned circuit tuned to 10.7 Mc/s.

B and C3 form a steady voltage source of the order of 12 volts, of low impedance at radio frequency.

The invention is not restricted to the details of the foregoing example. For instance, the Q of the rejector circuit may be reduced to say 10 or 20 but the inductance L2 is preferably sufficiently high almost to be tuned by the stray capacitancies. Two rejector circuits may be provided, tuned respectively to the second and third harmonics, but a single tuned rejector circuit is adequate for normal purposes. A diode type CV448 may be employed instead of type OA5, but the latter is pre-

#### WHAT WE CLAIM IS: -

1. Voltage limiting apparatus comprising a tuned tank circuit, having an impedance which is low except at its resonant frequency, and a biased diode or like rectifier device fed from the tank circuit through at least one rejector circuit tuned to a harmonic of the resonant frequency of the tank circuit.

2. A voltage limiting circuit substantially as hereinbefore described with reference to, and illustrated diagrammatically in, Figure 1, of the accompanying drawings.

BOULT, WADE & TENNANT, 111 & 112, Hatton Garden, London, E.C.1, Chartered Patent Agents.

### PROVISIONAL SPECIFICATION

## Improvements in or relating to Diode Limiters

We, CHARLES GILBERT MAYO, of 16, Christchurch Road, Purley, Surrey, EDMUND RAMSEY WIGAN, of "Kerry", Barnham, Sussex, and ROY EDWARD JONES, of 48, Kingscroft Road, Leatherhead, Surrey, all British subjects by birth, do hereby declare the invention to be described in the following

In circuit arrangements to which this invention can be applied the signal which is to be controlled appears in a tuned circuit, or "tank" circuit, which has an impedance which is low at all except one selected frequency. In the case of an F.M. receiver this would

be the carrier-frequency (or the equivalent frequency after passing through a frequencychanging stage). In these circumstances the tank

circuit tends to maintain the voltage wageform as a sinusoid in spite of any controlaciton introduced by the limiting diode; the

wave-form is not truncated, as would be the 105

case if the tank were absent.

A conventional arrangement of this kind of limiter, (commonly used to reduce the amplitude variation in an F.M. signal), consists of a diode, provided with a suitable biassing potential, and connected across the tuned circuit, or tank circuit. It is deficient in two

822,762

respects; first, the onset of the limiting action, when the peak amplitude of the signal reaches the designated threshold, is gradual and not sharply defined, and, second, even when the threshold is well passed the suppression of amplitude variation is far from complete. For this reason it has been found necessary in practice, where the highest degree of suppression is called for, to use more than one limiter.

It is now proposed to remove both these deficiencies by a modification to the diode circuit. The performance of a conventional limiter modified in this way can be made equal or superior to that of two conventional limiters in tandem, and is achieved by including in series with the diode one or more shunt tuned circuits set to reject harmonics of the tank-circuit resonant frequency. The inductance of a rejector circuit may, in practice be tuned by stray capacitance.

As in the conventional limiter the bias voltage for the diode may be provided from external sources or wholely or in part by the rectified current delivered by the diode itself.

C. G. MAYO, E. RAMSEY WIGAN, R. E. JONES.

Leamington Spa: Printed for Her Majesty's Stationery Office, by the Courier Press.—1959. Published at The Patent Office, 25, Southampton Buildings, London, W.C.2, from which copies may be obtained.

20

# 822,762 COMPLETE SPECIFICATION 2 SHEETS This drawing is a reproduction of

This drawing is a reproduction of the Original on a reduced scale.

SHEETS | & 2

822,762 COMPLETE SPECIFICATION

2 SHEFTS This drawing is a reproduction of

the Original on a reduce scale.

SHEETS 1 & 2